STM32 DMA

DMA

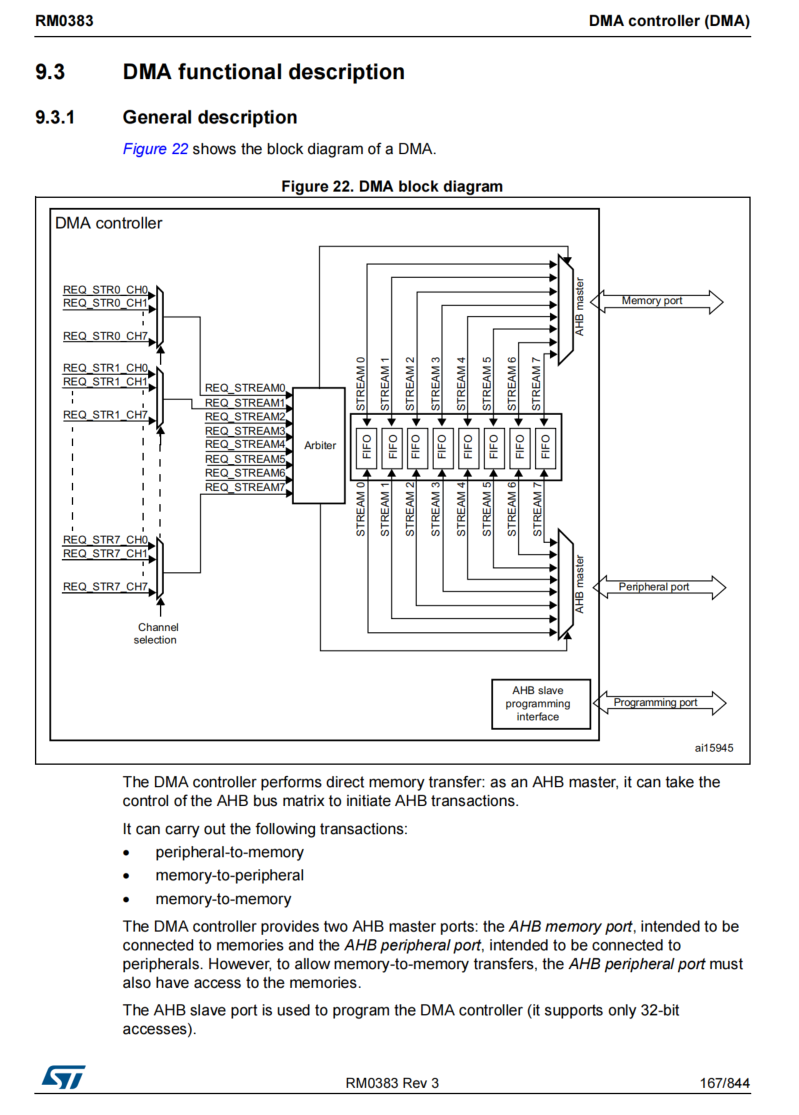

- DMA控制器在MCU内部是一个AMBA advcanced high-performance bus (AHB) Master。

- DMA控制器和AHB有三个接口:

- 一个Slave接口(用于CPU对它进行编程)

- 两个Master接口,允许将DMA去开启两个AHB总线上两个从设备之间的信号通信。

- 每个DMA都具有8个Streams

- 每个Stream都只能单向传输

- Steam可被配置的模式

- 从内存到外设

- 从外设到内存

- 从内存到内存

FIFO

FIFO可以作为一个临时缓存区,将数据暂时存储在队列中,以减少对内存或外设的频繁访问,提高系统的效率。

以DMA搬运串口接收到的数据为例,每来一个字节都要搬运一次,此时就会DMA占用从AHB总线到memory的总线,此时CPU就不能访问memory,或者CPU正在访问memory那么DMA就暂时不能将数据搬运过去,这样效率比较低。

FIFO的作用:

1,减少AHB带宽的占用,减少AHB总线的仲裁,让CPU能够在AHB总线上占用更大的带宽而不需要和DMA经常竞争总线。(DMA接收数据时可以旁路AHB总线)

2,减少溢出,在需要动态扩展内存时,DMA会暂存数据进入FIFO,给CPU执行动态扩展内存争取时间,防止溢出。

3、DMA多路Stream仲裁时,FIFO可以多路Stream缓冲,极大提高并发性。

单位 由8个位bit组成1个字节Byte;在一台8位机中,它的一个字就是一字节,一台16位机,它的一个字就是两字节,同理32位机一个字是4个字节;半字就是字的一半。

FIFO 每个数据流都独立拥有四级32位FIFO(先进先出存储器缓冲区)。FIFO的阈值, 分别为1/4、1/2、3/4和满,即分别为32位,64位,96位和128位。如果数据存储量达到阈值级别时,FIFO内容将传输到目标中。

PBURST[1:0]和MBURST[1:0]位是位于DMA_SxCR寄存器中的,用于分别设置外设和存储器不同节拍数的突发传输, 对应为单次传输、4个节拍增量传输、8个节拍增量传输和16个节拍增量传输。节拍取决于MSIZE或PSIZE。

参考资料:

1.CSDN

burst

Burst介绍:

DMA控制器可以生成单次传输或增量突发传输,传输的节拍数为4、8或16。

为了确保数据一致性,构成突发传输的每组传输都是不可分割的:AHB传输被锁定,AHB总线矩阵的仲裁器在突发传输序列期间不会撤销DMA主设备的授权。

作用:

可以通过Brust进行多个寄存器的同时修改,在M2P时同时配置多个定时器

https://shequ.stmicroelectronics.cn/thread-638925-1-1.html

仲裁机制

当同时使用多个stream流时,首先根据初始化时设定的优先级进行排序(软件),优先级高的先执行,如果优先级相同,那么根据stream*,即stream流本身的数字大小,小的先执行,比如stream1和stream2为相同优先级,那么stream1先运行。